一种基于专用DSP芯片,采用独特的软件抗噪声算法的数字抗噪声模块,实现了在120分贝噪声环境中话音的清晰度不小于98。此模块已成功应用于我国航天机载通讯设备及工业防爆扩音广播呼叫系统。

概 述:

国内目前第三代抗噪声产品是利用动态降噪(DNR)技术。DNR技术是通过变化的话音峰值动态地调节输出话音开关,从而达到降噪的目的。它虽然是目前较好的一种抗噪声模拟处理技术,但存在一些局限性,包括轻符音掉字和强音噪声拖尾;降噪效果偏重于低频;降噪完全采用硬件电路实现,调试和维修比较麻烦等问题。由于存在这些问题,致使模拟DNR降噪产品的大量推广应用受到限制。随着数字信号处理技术的迅速发展,以数字信号处理器及其相关算法为技术支撑的数字抗噪声技术的产品不断涌现。替代了DNR模拟降噪技术产品。数字抗噪声技术就是应用现代数字信号处理(DSP)技术及其高速实时处理运算的特性,采用相应的软件算法,对高噪声环境中的话音和噪音进行处理,完成高噪声环境中的语音通信功能。

本数字降噪模块的性能优点包括

a) 软件采用自适应滤波算法,数字抗噪声处理器对噪声的抑制量一般在50分贝以上,而且出话音平稳,无漏字和噪声拖尾现象。

b) 数字抗噪声处理器在整个话音频带内(300~3000Hz)降噪量均衡。

c) 数字抗噪声处理器可通过改变软件算法满足不同的抗噪声要求,便于产品升级换代。

d)硬件成本比模拟DNR产品更低。

e)采用软件加密技术,产品不易被侵权、仿造,有利于保护生产厂家的利益。

主要指标要求及总体设计方案

数字抗噪声处理模块主要用于航天机载通讯终端设备及工业扩音广播呼叫系统等高噪声环境中的通讯联络,如扩音广播呼叫话站、电话机、送受话器、呼叫设备。其送话频率范围为300~3400Hz,平坦度不大于2dB。降噪性能为:模块输入端加入3mV、2秒断续的正弦波信号(频率依次为300Hz、700Hz、1000Hz、1500Hz、2000Hz、2500Hz、3000Hz)与加入3mV、120dB持续的白噪声信号时,模块输出电平之差不小于50dB。首先要选用一款合适的DSP器件。要求具有低功耗、高速数据运算和吞吐能力(40 MIPS以上),内含A/ D、D/ A、Flash闪存(16KB)。然后建立有效的噪声模型,设计自适应滤波结构及其相关软件算法。接下来设计数字抗噪声处理器的电磁兼容性(EMC),选用能适应120dB环境噪声的抗噪声送话器器件。DSP硬件与相关软件算法结合,使数字抗噪声处理器在120dB高噪声环境下,达到话音清晰度不小于98%

软硬件设计方案

主要工作原理

数字抗噪声处理模块主要完成高噪声环境下话音的高清晰度通信功能。话音信号和环境噪声通过MIC输入到前置放大级,前置放大级的作用是把话音和环境噪声放大到专用DSP芯片内的A/D能识别的幅度,以便A/D能正常转换信号,模拟信号通过A/D转换后变成12位的数字信号进入DSP的运算单元,DSP在前3秒钟内完成测试周围环境噪声的大小并建立数学模 型,然后按给定的算法处理话音和噪声,把处理结果通过数据总线送到D/A,经平滑滤波后送入后级放大器,后级放大器的 作用是为了满足关联设备输入要求。

DSP芯片选择

数字抗噪声处理模块对数字信号处理器芯片的要求较高。芯片既要有很强的实时处理性能,又要有很高的运算速度和数据吞吐能力;还要求功耗低,外部的A/ D、D/ A及Flash闪存最好集成在DSP内部,以减小产品体积。所以,选用TMS320C5XX系列DSP芯片中的一款作为处理芯片,外配高速A/ D、D/ A及32KB Fl a s h作程序加载。

软件算法方案

数字抗噪声处理器是由自适应滤波器来实现的。自适应滤波器具有跟踪信号和噪声变化的能力,使滤波器的特性也随信号和噪声的变化而变化,以达到最优滤波效果。自适应滤波器的特性变化是由自适应算法通过调整滤波器权系数来实现。一般情况,自适应滤波器由两部分组成,一是滤波器结构,二是调整滤波器系数的自适应算法。自适应滤波器的结构采用FIR结构。对带内白噪声的处理用经典的LMS算法还不能达到最优的降噪效果,还要利用噪声的自相关特性和功率谱密度特性,在LMS算法的基础上作适当修整才能达到最佳的降噪效果。

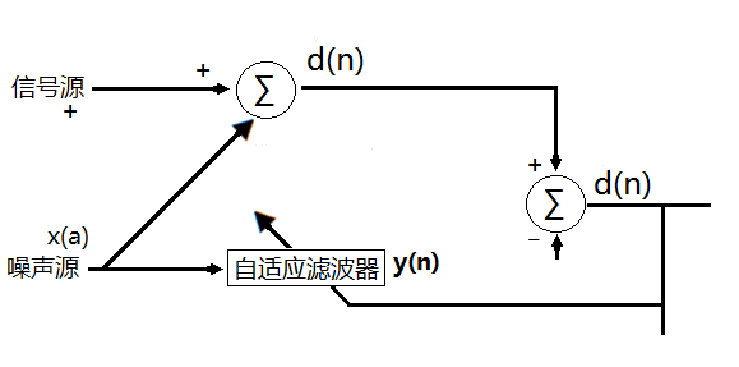

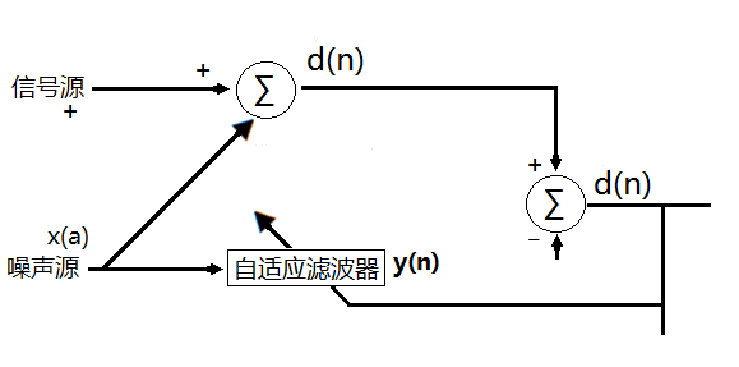

数字式抗噪声送话器组的DSP实现结构如图1所示。原始输入信号d(n)包括信号和噪声,x(n)为参考噪声输入。这种自适应滤波器实质上是完成d(n)中的噪声估计,并把估计值y(n)与原始信道相减以达到噪声消除的结果,当然,估计值y(n)与原始输入信号并不是简单的代数相减,而是有一套相应的软件算法,如相关功率的功率谱分析等。图1中,自适应滤波器采用横向型结构,滤波器的输出y(n)

表示为:y(n)= ∑ Wi (n- i) i =0 N为滤波器的阶数。

软件设计:

一个自适应滤波器实现的复杂性通常是由它所需要的乘法次数和阶数来衡量。基于DSP实现的自适应滤波器系统,其DSP芯片的数据吞吐量和数据处理速度也相当重要。本数字抗噪声处理器采用了120阶自适应数字滤波器,选用了运算速度为40MIPS的DSP芯片作为主处理器,由于该DSP芯片内包含A/ D和D/ A及16KB的f l a s h存储器,这些片内资源使自适应滤波器的实现更有效。根据噪声的自相关特性和功率密度性,软件上除采用了传统对称横向结构的FIR滤波器中的LMS算法外,还对噪声和信号的功率谱密度进行估计,即对采样编码的16个值进行平方累加,求出其平均功率值,与前一样点功率值进行比较,比较后的差值与设定的噪声门限值进行相除,结果若大于1,则调整滤波器的权系数变小,信号输出幅度变大,若结果小于等于1,则滤波器的权系数变大,信号输出幅度变小。

定制专用抗噪声DSP芯片调试工作完成后,交给专门制作DSP芯片的公司作成一片具有抗噪声功能的DSP专用芯片。经过实测,整机的耗电不大于70mA,DSP芯片的引出脚缩减到64引脚,大大减小了印刷电路板的面积。由于软件代码一次性掩膜在芯片内,免去了每次都写入代码的麻烦,减少了调试的工作量。一般情况下,模块只要调试3个点就可完成,大大降低了调试成本,有利于批量生产。

结语

数字抗噪声模块使用DSP芯片,利用自适应技术,既提高了通信产品的抗噪性能,又降低了生产成本。该模块已成功应用于我国机载通讯设备及工业防爆扩音广播呼叫系统。

当前位置:首页 > 技术指导

当前位置:首页 > 技术指导